マルチプレクサとは、2n本の入力線と1本の出力線を持つ組み合わせ回路である。 簡単に言うと、マルチプレクサは多入力1出力の組合せ回路である。 入力線から2値情報を受け取り、出力線に導く。 選択ラインの値に基づいて、これらのデータ入力の1つが出力に接続されます。

エンコーダやデコーダと異なり、選択ラインはn本、入力ラインは2n本です。 つまり、入力の組み合わせは全部で2N通りあります。

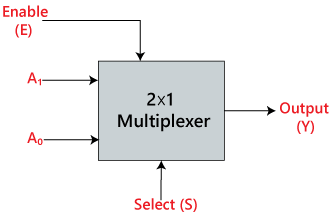

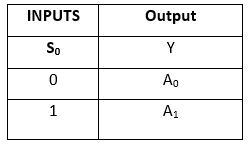

マルチプレクサには、次のような種類があります。 選択線S0に存在する入力の組み合わせに基づいて、これら2つの入力のうちの1つが出力に接続される。 2×1マルチプレクサのブロック図と真理値表を以下に示す。

ブロック図:

真理値表:

項Yの論理式は次の通り:

Y=S0′.A0+S0.A1

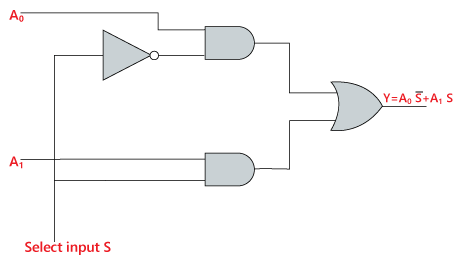

上記式の論理回路を以下に示す:

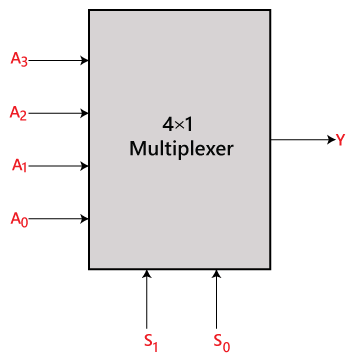

4×1 Multiplexer:

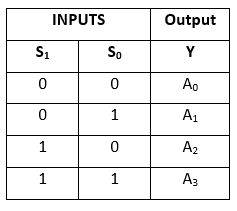

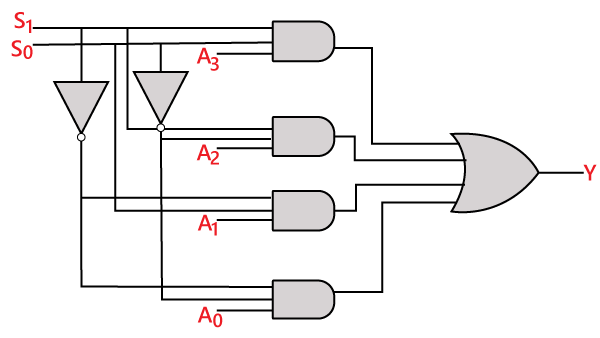

4×1マルチプレクサにおいて、合計4つの入力、すなわち。 選択線S0とS1に存在する入力の組み合わせに基づいて、これら4つの入力のうちの1つが出力に接続されます。 この4×1マルチプレクサのブロック図と真理値表は次のとおりです。

ブロック図:

真理値表:

項Yの論理式は、次のようになる。

Y=S1′ S0′ A0+S1′ S0 A1+S1 S0′ A2+S1 S0 A3

上記式の論理回路を以下に示す:

8 to 1 Multiplexer

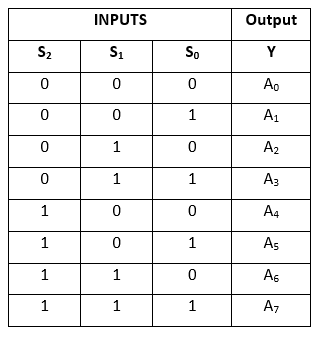

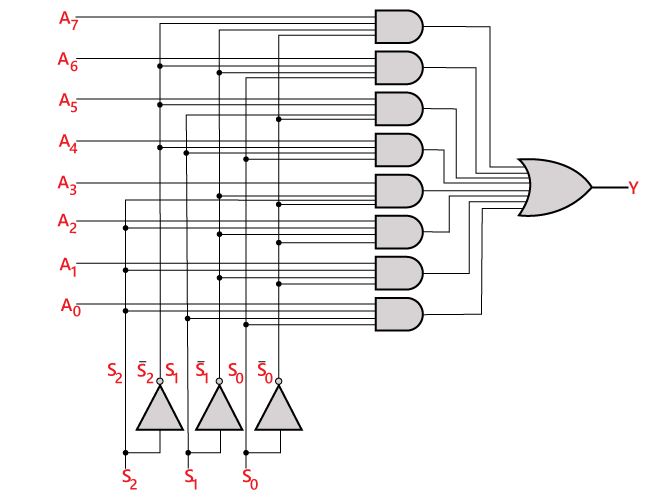

8 to 1マルチプレクサにおいて、合計8入力、すなわち、1入力が存在します。e., A0、A1、A2、A3、A4、A5、A6、A7、S0、S1、S2の3つの選択線、Yの1つの出力があり、選択線S0、S1、S2に存在する入力の組み合わせに基づいて、これら8入力のうちの1つが出力に接続されています。 8×1マルチプレクサのブロック図と真理値表を以下に示す。

ブロック図:

真理値表:

項Yの論理式は以下の通りである:

Y=S0′.S1′.S2′.A0+S0.S1′.S2′.A1+S0′.S1.S2′.A2+S0.S1.S2′.A2> 真理値表は以下の通りである。A3+S0′.S1′.S2 A4+S0.S1′.S2 A5+S0′.S1.S2 .A6+S0.S1.S3.A7

上式の論理回路は次のようになります。

4×1 と 2×1 マルチプレクサによる 8×1 マルチプレクサ

下位マルチプレクサを用いて 8×1マルチプレクサを実装できるようにします。 8×1マルチプレクサを実装するためには、2つの4×1マルチプレクサと1つの2×1マルチプレクサが必要です。 4×1マルチプレクサは、2本の選択線と4つの入力と1つの出力を持つ。 2×1マルチプレクサは選択線が1本だけです。

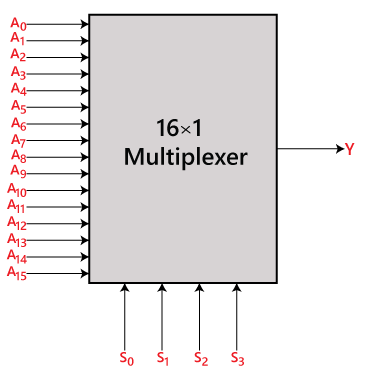

8つのデータ入力を得るには、2つの4×1マルチプレクサが必要です。 4×1マルチプレクサは、1つの出力を生成します。 したがって、最終的な出力を得るためには、2×1マルチプレクサが必要です。 以下に、4×1および2×1マルチプレクサを使用した8×1マルチプレクサのブロック図を示します。 選択ラインS0、S1、S2に存在する入力の組み合わせに基づいて、これら16の入力のうちの1つが出力に接続されます。 16×1

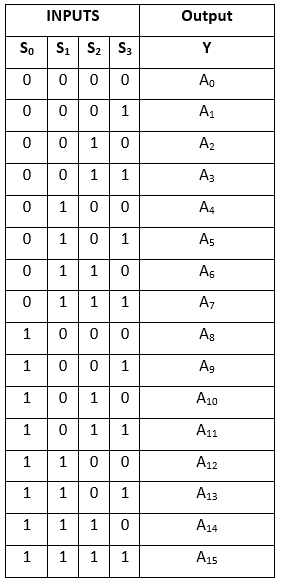

のブロック図と真理値表:

真理値表:

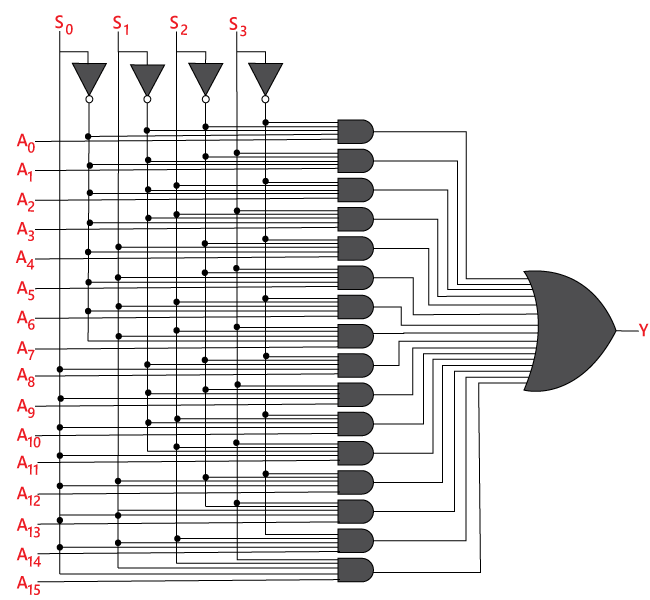

項Yの論理式は、次のようになる。

上記式の論理回路を以下に示す:

8×1と2×1のマルチプレクサを用いた16×1マルチプレクサ

低次マルチプレクサを用いて16×1マルチプレクサを実装することができます。 8×1マルチプレクサを実装するためには、8×1マルチプレクサ2個と2×1マルチプレクサ1個が必要です。 8×1マルチプレクサは、3本の選択ライン、4つの入力、1つの出力を備えています。 2×1マルチプレクサは選択線が1本だけです。

16個のデータ入力を得るには、2つの8×1マルチプレクサが必要です。 8×1マルチプレクサは、1つの出力を生成します。 したがって、最終的な出力を得るためには、2×1マルチプレクサが必要です。 以下に、8×1と2×1マルチプレクサを使用した16×1マルチプレクサのブロック・ダイアグラムを示します。